# An independent loops search algorithm for solving inductive PEEC large problems

T-S. Nguyen, J-M. Guichon, O. Chadebec, G. Meunier, B. Vincent Grenoble Electrical Engineering Laboratory, University of Grenoble Grenoble-INP / Université Joseph Fourier / CNRS UMR 5269, Grenoble, France

Abstract —This paper describes an original approach for determining independent loops needed for mesh-current analysis in order to solve circuit equation system arising in Partial Element Equivalent Circuit (PEEC) approach. Presented algorithm is well–suited for large degrees of freedom problems, saving significantly memory and decreasing the time of resolution.

#### I. INTRODUCTION

Node-voltage and Mesh-current analysis are two powerful methods which simplify circuit analysis substantially. However, let us point out that nodal analysis is unsuitable for circuits with many mutual inductances such as those provided by inductive low frequency PEEC method. In such cases, only independent loop analysis could reduce the circuit equations into the smallest number of unknowns and also provided a much better condition number for the system than those given by standard Kirchhoff's equations [1]. Despite this clear advantage, this approach requires to identify an independent set of independent loops (or mesh), which is well known for being an uneasy task.

Many strategies has been proposed to determine independent loop matrix, such as general matrix solution by inspection of the circuit [2] or graph algorithms [3][4]. Method proposed in [2] is extremely time and memory consuming for complicated 3D structures due to the use of large scale matrix calculation and storage. The approach in [4] has better performance than the generic graph solution proposed in [3] but its drawback is the dependence with the geometry discretization.

In this paper, a novel strategy coupling a general loop matrix method with a simple graph algorithm is presented. The proposed method is a generic circuit solution such as [2][3] and requires similar computational complexity as [4]. An industrial application with 11,445 branches has been treated using our method.

# II. PEEC MESH CURRENT PRINCIPE

### A. Equivalent circuit formulation

By assuming quasi-static conditions and without any magnetic material, the classical PEEC method is derived from the equation governing the total electric field at a point r inside the conductors:

$$\frac{\mathbf{J}(\mathbf{r})}{\sigma} + j\omega \frac{\mu_0}{4 \cdot \pi} \iiint_{v} \frac{\mathbf{J}(\mathbf{r}')}{|\mathbf{r} - \mathbf{r}'|} dv = -\nabla \phi(\mathbf{r})$$

(1)

where J is the current density,  $\phi$  is the scalar electric potential,  $\sigma$  is the material conductivity,  $\mu_0$  is the vacuum permeability and  $\omega$  is the excitation pulse.

To compute the current in each branch, a mesh-based analysis is used [1], where mesh is set of independent loop of branches in the graph representing the circuit. We can change (1) into a new equation:

$$\mathbf{MZ_bM^tI_m} = \mathbf{Z_mI_m} = \mathbf{MV_b} = \mathbf{V_s}$$

(2)

where  $\mathbf{Z}_b$  is a complex branch impedance matrix,  $\mathbf{Z}_m$  is a complex loop-based impedance matrix,  $\mathbf{I}_m$  is a vector independent loop-based currents,  $\mathbf{M}$  is the transition matrix (branch – independent loop matrix) where each element is equal to -1, 0 or 1,  $\mathbf{V}_s$  is the vector of source voltages (most part of time equal to 0). Expression to compute each element in  $\mathbf{Z}_b$  can be found in [1]. Let us notice that one fundamental loop may be composed of geometrical PEEC filament and external electric component (R, L, C, source current, source voltage)

## B. Graph partition for independent loops identification

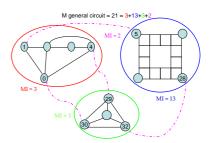

In this paper, the general circuit denotes the PEEC circuit, a sub-circuit is a group of independent loops and the circuit connecting all sub-circuit will be called super-circuit. The general circuit is then composed of sub-circuits and a super-circuit. The union of these both sets of independent loops is the complete set of independent loops of the general circuit (see Fig. 1). So if *m* denotes the number of independent loops:

$$m_{general\_circuit} = m_{\sup er-circuit} + \sum_{all\_sub-circuit} m_{sub-circuit}$$

(3)

Fig. 1. Union of two set of loops in PEEC network

To identify all of fundamental loops, we have to:

- Step 1: Partition general circuit into several sub-circuits and detects all fundamental loops in each of them.

- Step 2: Create the super-circuit from general circuit and sub-circuits and then search all fundamental loops in it.

The partitioning of the general circuit into sub-circuits and super-circuit will be described in the next section.

#### III. IDENTIFICATION FUNDAMENTAL LOOPS ALGORITHM

#### A. Sub-circuits determination and their loops analysis

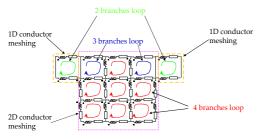

A very efficient way to search independent loops is to look for loops with the minimum number of branches. We want to determine all loops having k branches at the most. In a typical PEEC discretization, most part of independent loops is composed of 4 branches (see Fig. 2) so we chose k=4 to be sure that a large number of loops would be found rapidly.

Fig. 2. Small loop of PEEC conductor meshing

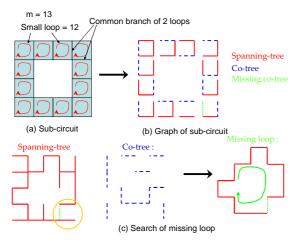

A Sub-circuit can be created by regrouping all small loops (with less than k branches) which share at least one branch with another small loop (see Fig. 3a). At the end of the process, some fundamental loops in the sub-circuit can miss. It remains to identify them.

To complete the missing loops, a graph algorithm is used to find the large-loops (with more than k branches) in the sub-circuit. An important number of loops has been already found, then building a spanning tree is very fast. The missing co-tree denotes the part of co-tree corresponding with missing loops. From this spanning tree and missing co-tree, all missing loops are determined thanks to *Breath First Search algorithm* (BFS) (see Fig. 3b, c).

Fig. 3. Sub-circuit loop analysis

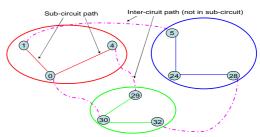

#### B. Super-circuit loop analysis

In step 2, we need to search a sub-circuit internal path linking its connections with the super-circuit (see Fig. 4). This task is achieved thanks to BFS algorithm. Once all the paths have been found, a super-circuit is created, composed of the sub-circuit internal path and the branches which have

been not included in sub-circuits. So, since this circuit has been reduced, the general matrix solution [2] is efficient to identify the last fundamentals loops.

Fig. 4. Reduction of general circuit to super-circuit

#### IV. NUMERICAL RESULT

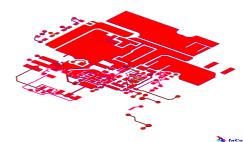

Classical general matrix solution technique has been compared with this new approach. Both techniques have been implemented in commercial InCa3D software [5]. A LED headlight PCB with 11,445 branches and 4,762 fundamental loops has been modeled. The result in Table 1 highlights the efficiency of the new method.

Fig. 5. Car Headlight LED PCB modeling in InCa3D (courtesy of Valeo)

TABLE I

Time for determining a set of independent loop

|         | Classical general matrix solution [2] | New algorithm |

|---------|---------------------------------------|---------------|

| Time(s) | 2894 s                                | 2.1 s         |

With our new approach, the total time for the current distribution computation is 85s (PC Intel Core 2 Duo @2.66Ghz - 2GB memory). The independent loops search algorithm is combined with an Adaptive Multi-Level Fast Multipole Method. 2.5s are needed to analyze the circuit, 7.5s to compute the near interactions, 75s for the iterative solving process. The memory requirement does not exceed 240 MB.

# v. References

- [1] M. Kamon et al, "Preconditioning techniques for constrained vector potential integral equations, with application to 3-D magnetoquasistatic analysis of electronic packages," in *Proceedings* of the Colorado Conference on Iterative Methods, April 1994.

- [2] L. T. Pillage et al Electronic Circuit and System Simulation Methods, McGraw-Hill Inc., 1995, pp. 371-381.

- [3] A. Rong et al, "A novel graph partitioning technique for enhancing the computational efficiency of the loop-tree generalized PEEC modeling of 3D interconnects," in *IEEE 14<sup>th</sup> Topical Meeting on Elect. Performance of Electron. Packaging*, 2005, pp. 253-256.

- [4] G. Antonini et al, "Hybrid Formulation of the Equation Systems of the 3-D PEEC Model Based on Graph Algorithms," *IEEE Trans. Circuits and Syst.-I: Reg. Papers*, vol. 57, no. 1, Jan. 2010

- [5] [Online] InCa3D Software www.cedrat.com